## Internal BJT Low Standby-Power Primary-side Converter

#### **General description**

The PN8571P consists of a Low Standby-Power Primary-Side controller and BJT, specifically designed for a high performance AC/DC charger or adaptor with minimal external components.

PN8571P operates in primary-side sensing and regulation, so opto-coupler and TL431 could be eliminated. In CV mode, multi-mode technique is utilized to achieve high efficiency, avoid audible noise and make the system meeting Energy star level VI. Good load regulation is achieved by the built-in cable drop compensation. In CC mode, the current and output power setting can be adjusted externally by the sense resistor at CS pin.

PN8571P offers complete protections including Cycle-by-Cycle current limiting protection (OCP), over voltage protection (OVP), open loop protection (OLP), over temperature protection (OTP) and CS open or short protection (CS O/SP) etc.

### Application

- Switch AC/DC Adapter

- Battery Charger

- Set-top box power supply

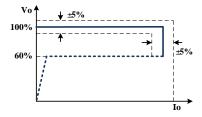

#### **Output Features**

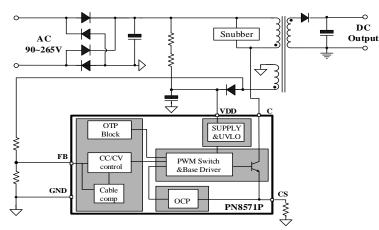

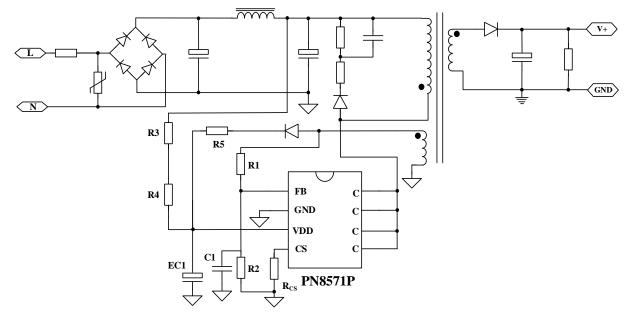

## **Typical Circuit**

#### Features

- Internal BJT switch

- Multi-mode technique

- ±5% CC Regulation at Universal AC input

- Primary-side Sensing and Regulation without TL431 and Opto-coupler

- Programmable Cable Drop Compensation

- No-need Control Loop Compensation Capacitor

- Excellent Protection include:

- $\diamond$  Over Temperature Protection (OTP)

- VDD Under/Over Voltage Protection(UVLO&OVP)

- ♦ Cycle-by-Cycle Current Limiting (OCP)

- ♦ CS Short/Open Protection (CS O/SP)

- ♦ Open Loop Protection(OLP)

## Package/Order Information

| Order code    | der code Package Typi |                       |

|---------------|-----------------------|-----------------------|

|               |                       | 90~265V <sub>AC</sub> |

| PN8571PSEC-R1 | SOP8                  | 12W                   |

www.chipown.com

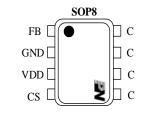

## **Pin Definitions**

| Pin Name | Pin Number | Pin Function Description                                                                                                     |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------|

| FB       | 1          | The voltage feedback from auxiliary winding. Connected to resistor divider from auxiliary winding reflecting output voltage. |

| GND      | 2          | Ground                                                                                                                       |

| VDD      | 3          | Power supply                                                                                                                 |

| CS       | 4          | Current Sense Input                                                                                                          |

| С        | 5,6,7,8    | HV BJT collector pin                                                                                                         |

## **Typical Power**

| Part number | Destroza | Adapter <sup>(1)</sup> |

|-------------|----------|------------------------|

|             | Package  | 90~265V <sub>AC</sub>  |

| PN8571P     | SOP8     | 12W                    |

Note:

1. Maximum output power is tested in an adapter at 40  ${\rm C}$  ambient temperature, with enough cooling conditions.

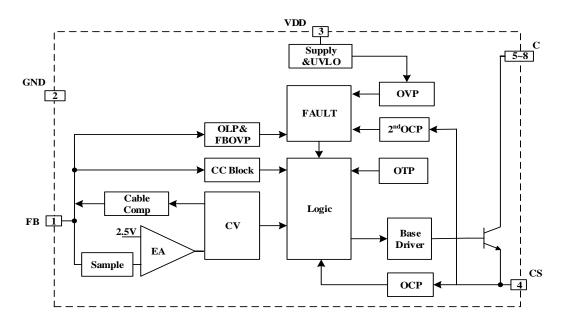

## **Block Diagram**

## **Absolute Maximum Ratings**

| Supply voltage Pin VDD          | -0.3~40V |

|---------------------------------|----------|

| $Pin FB(I_{FB} \le 10mA) \dots$ | 1~5.5V   |

| Pin CS                          | 0.3~5.5V |

| CB voltage                      | 700V     |

| Operating Junction Temperature  | 40~150 ℃ |

| Storage Temperature Range55~15                                            | 0 °C |

|---------------------------------------------------------------------------|------|

| Lead Temperature (Soldering, 10Secs)26                                    | 0 °C |

| Package Thermal Resistance $\theta_{JC}$ (SOP8)40 ${}^{\circ}\!\!{\rm C}$ | /W   |

| HBM ESD Protection <sup>(1)</sup> ±                                       | 3kV  |

Note:

1. Test standard: ANSI/ESDA/JEDEC JS-001-2017.

## **Electrical Characteristics**

$(T_A=25 \text{ C}, \text{VDD}=21 \text{V}, \text{ unless otherwise specified})$

| PARAMETER                                | SYMBOL                    | CONDITIONS                              | MIN.  | ТҮР. | MAX. | UNIT |

|------------------------------------------|---------------------------|-----------------------------------------|-------|------|------|------|

| Power Section                            |                           |                                         |       |      |      | •    |

| Collector-base breakdown voltage         | Vcbo                      | Ic=10mA                                 | 700   |      |      | V    |

| Collector-emitter<br>breakdown voltage   | VCEO                      | I <sub>C</sub> =10mA, I <sub>B</sub> =0 | 400   |      |      | V    |

| Collector Peak Current                   | Ic                        |                                         |       |      | 0.75 | А    |

| Supply Voltage Section                   |                           |                                         |       |      |      |      |

| Operating voltage range                  | VDD                       |                                         | 9.5   |      | 30   | V    |

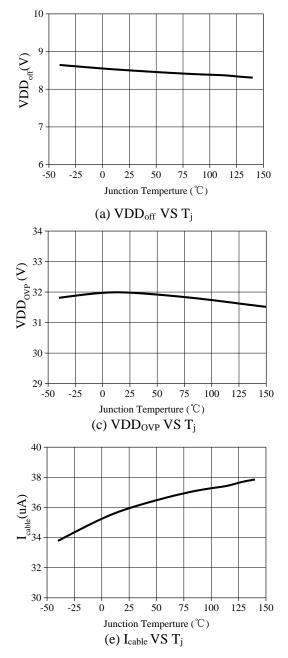

| VDD start up threshold                   | VDD <sub>on</sub>         |                                         | 14.5  | 16.5 | 18.5 | V    |

| VDD under voltage shutdown threshold     | VDD <sub>off</sub>        |                                         | 7.5   | 8.5  | 9.5  | V    |

| VDD over voltage protect                 | VDD <sub>ovp</sub>        |                                         | 30    | 32   | 35   | V    |

| Supply Current Section                   |                           |                                         |       |      |      |      |

| VDD charge current                       | Idd_startup               | VDD=VDDon - 0.5V                        |       | 3    | 5    | uA   |

| Operating current,<br>switching          | Idd                       | $VDD = VDD_{on} + 1V$                   | 0.1   | 0.6  | 0.8  | mA   |

| Operating current after fault            | I <sub>DD_FAULT</sub>     | VDD=15V after fault                     |       | 0.5  |      | mA   |

| Current Sense Section                    |                           |                                         |       |      |      |      |

| Current sense threshold                  | $V_{TH\_OC}^{(1)}$        |                                         | 485   | 500  | 515  | mV   |

| Maximum Current sense threshold          | VTH_OC_MAX <sup>(1)</sup> |                                         |       | 560  |      | mV   |

| Minimum CS threshold                     | Vcs_min                   |                                         |       | 170  |      | mV   |

| Leading Edge Blanking time               | $T_{LEB}$                 |                                         |       | 300  |      | ns   |

| Maximum Ton                              | Tonmax                    |                                         | 32    | 40   | 50   | us   |

| OCP propagation delay                    | Td_oc                     |                                         |       | 100  |      | ns   |

| FB Section                               |                           | •                                       |       |      | ·    |      |

| Reference voltage for feedback threshold | V <sub>REF_CV</sub>       |                                         | 2.455 | 2.48 | 2.52 | v    |

| Output over voltage protection threshold | Vfbovp                    |                                         | 2.85  | 3    | 3.15 | v    |

| Output under voltage threshold           | $V_{UVP}$                 |                                         |       | 1.55 |      | V    |

| Maximum cable<br>compensation current    | Icable                    | V <sub>FB</sub> =0V                     | 33    | 36   | 39   | uA   |

| PARAMETER                                        | SYMBOL              | CONDITIONS             | MIN. | TYP. | MAX. | UNIT |

|--------------------------------------------------|---------------------|------------------------|------|------|------|------|

| Minimum Toff                                     | $T_{\text{offmin}}$ |                        |      | 5    |      | us   |

| Maximum Toff                                     | Toffmax             |                        |      | 2.2  |      | ms   |

| Output under voltage<br>protection Blanking time | $T_{UVP}$           | F <sub>s</sub> = 50kHz | 40   |      | 64   | ms   |

| Thermal Section                                  |                     |                        |      |      |      |      |

| Thermal shutdown<br>temperature threshold        | T <sub>SD</sub>     |                        | 135  | 150  |      | C    |

| Thermal shutdown<br>hysteresis                   | Thyst               |                        |      | 30   |      | C    |

Note:

(1)This parameter is the real measurable value of circuit delay and switch delay, which should be considered in the actual test and design.

Chipown

## **Typical Characteristics Plots**

# PN8571P

### **Functional Description**

The PN8571P is a high performance CC/CV primary-side controller. PN8571P operates in primary-side sensing and regulation, so opto-coupler and TL431 could be eliminated. Proprietary built-in CV and CC control can achieve high precision CC/CV control meeting most charger and adapter application requirements. Startup current of PN8571P is designed to be very low so a large value startup resistor can be used to minimize the power loss in application.

#### 1. Start up Control

At start up, external startup resistor charges the VDD capacitor via VDD pin. When VDD reaches VDD<sub>on</sub>, the device starts switching. The device keeps in normal operation provided as long as VDD keeps above VDD<sub>off</sub>. After startup, the bias is supplied from the auxiliary transformer winding.

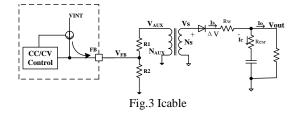

#### 2. CC Operation Mode

In CC operation mode, the PN8571P captures the auxiliary flyback signal at FB pin through a resistor dividing-network. The pulse width of the auxiliary flyback signal determines the PN8571P oscillator frequency. The higher the output voltage is, the shorter the pulse width is, and the higher the chip oscillator frequency is, thus the constant output current can be achieved.

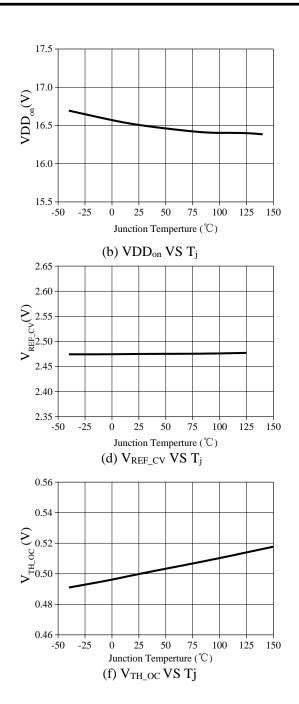

The current waveform in DCM mode is shown in Fig.1. During BJT turn-on time, the current in the primary winding (Ipri) ramps up. When BJT turns off, the energy stored in the primary winding is transferred to the secondary side, so the peak current in the secondary winding is

$$I_{\text{sec}_pk} = I_{pri_pk} \times N_{ps} \tag{1}$$

The output average current is

$$I_{O} = \frac{I_{\text{sec}\_pk}}{2} \times \frac{T_{demag}}{T_{P}} = \frac{1}{2} N_{PS} \frac{V_{CS}}{R_{sense}} \frac{T_{demag}}{T_{P}} \quad (2)$$

Where Rsense means system resistor at CS pin,  $N_{PS}$  means primary winding and secondary winding turn ratio.

In CC mode, PN8571P fixes  $\frac{T_{demag}}{T_P}$  to be 0.5, and V<sub>cs</sub> to be

$V_{TH_{OC}}$  (typically 0.5V, actually about 0.58V considering the affection of system and delay time). Meanwhile, assuming the current coupling ratio is Kc, the output current will be constant as:

$$I_0 = \frac{1}{4} N_{PS} \frac{0.58}{R_{sense}} \times \text{Kc}$$

(3)

Fig.1 The current waveform in DCM mode

#### 3. CV Operation Mode

In CV mode, PN8571P uses a pulse to sample  $V_{FB}$  and it is hold until the next sampling. The sampled voltage is compared with  $V_{REF_CV}$  and the error is amplified. The error amplified output reflects the load condition and controls the switching off time to regulate the output voltage, thus constant output voltage can be achieved.

The relationship between the output voltage and V<sub>REF\_CV</sub> is

$$Vo = (V_{REF_{CV}} \times \frac{R1 + R2}{R2}) \times \frac{N_s}{N_{AUX}}$$

(3)

$N_s$  means Secondary winding truns,  $N_{AUX}$  means Auxiliary winding truns.

The PN8571P operates in PFM mode during full load mode, since the peak current (Ipeak) of BJT is constant, the chip frequency decreases while the output current decreases. When the switching frequency approaches to 25kHz, the PN8571P enters PWM mode, the chip frequency decreases slowly while the output current decreases, the Ipeak decreases while the output current decreases. Therefore the PN8571P can avoid audible noise, while achieving high efficiency at 25% load conditions. When Vcs decreases to 170mV, the PN8571P enters Standby mode. In this mode, Ipeak keeps around constant, the chip oscillator frequency decreases while the output current decreases. Fig.2 illustrates the relations of the switching frequency, Ipeak and Loading for PN8571P.

Fig.2 The Switching Frequency, V<sub>CS</sub> VS. LOAD

## 4. Current Sensing and Leading Edge Blanking

Cycle-by-Cycle current limiting is offered in PN8571P. The switch current is detected by a sense resistor at CS pin. The CC set-point and maximum output power can be externally adjusted by external current sense resistor at CS pin. An internal leading edge blanking circuit chops off the sensed voltage spike at initial power BJT on-state so that the external RC filtering on sense input is no longer needed.

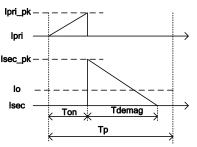

#### 5. Programmable Cable Drop Compensation

In PN8571P, an offset voltage is generated at FB pin by an internal current flowing into the divider resister, as shown in Fig.3. The Cable Drop Compensation block compensates the voltage drop across the cable. As the load current decreases from full load to no load, the voltage drop across the cable decreases. It can be programmed by adjusting the external resistor R2 or R1 at FB pin. The maximum compensation is

$$\frac{V_{cable}}{V_{O}} = \frac{I_{cable} \times (R2 // R1)}{2.5V}$$

(4)

Because of the influence of the chip's sampling position and devices of the system, the actual maximum compensation is less than theoretical value.

#### 6. Protection Control

The PN8571P has several self-protection functions, such as Cycle-by-Cycle current limiting (OCP), Over-Voltage Protection, Over-Temperature Protection, Feedback Loop open Protection, Output short circuit Protection, CS resistor open/short circuit Protection and Under Voltage Lockout on VDD. All protections are self-recovered.

# PN8571P

## **Typical Application**

#### **Component Parameter and Layout Considerations:**

- 1. VDD capacitor EC1 should be placed at the nearest place between the VDD pin and the GND pin.

- 2. It is suggested that the power supply diode and the R5 should be connected in series in order to improve the safety capability. The recommend value is 4.70hm.

- 3. It is suggested that the FB pin and the C1 should be connected in parallel in order to improve the anti-interference of the sampling network. The recommend value is 47pF.

- 4. Choose CS resistance reasonably to avoid IC exceeding 0.75A.

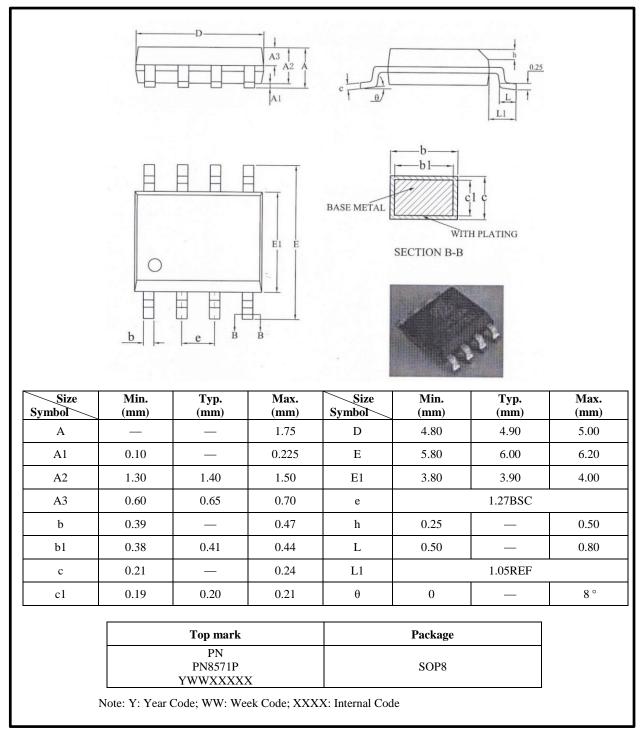

## **Package Information**

#### **Package Information SOP8**

Notes:

1. This drawing is subjected to change without notice.

2. Body dimensions do not include mold flash or protrusion.

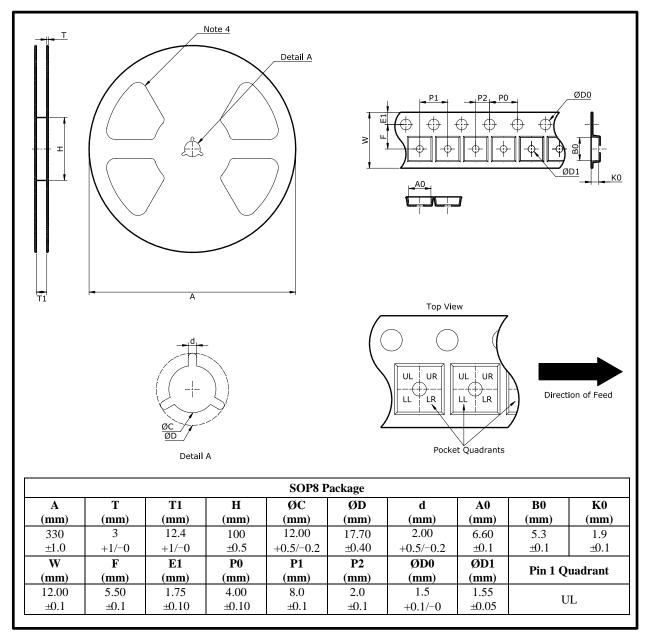

## **Tape and Reel Information**

Notes:

1. This drawing is subjected to change without notice.

2. All dimensions are nominal and in mm.

3. This drawing is not in scale and for reference only. Customer can contact Chipown sales representative for further details.

4. The number of flange openings depends on the reel size and assembly site. This drawing shows an example only.

## **Important Notice**

Wuxi Chipown Microelectronics Co. Ltd. reserves the right to make changes without further notice to any products or specifications herein. Wuxi Chipown Microelectronics Co. Ltd. does not assume any responsibility for use of any its products for any particular purpose, nor does Wuxi Chipown Microelectronics Co. Ltd assume any liability arising out of the application or use of any its products or circuits. Wuxi Chipown Microelectronics Co. Ltd does not convey any license under its patent rights or other rights nor the rights of others.